Tecnologías avanzadas de encapsulado de semiconductores

Las tecnologías avanzadas de envasado de semiconductores son cruciales debido a la ralentización de la ley de Moore y al aumento de los costes de desarrollo y fabricación de circuitos integrados monolíticos de silicio. Al principio, los componentes se encapsulaban individualmente y se integraban a nivel de placa de circuito impreso, pero a medida que los dispositivos se hacen más pequeños y requieren mayores capacidades de procesamiento, la integración de componentes debe ir más allá del nivel de placa.

La integración a nivel de encapsulado fue el primer avance, seguido de la integración a nivel de oblea, que proporciona una densidad de conexiones al menos diez veces mayor, una huella más pequeña adecuada para aplicaciones sensibles al tamaño y un rendimiento superior.

La integración a nivel de oblea abarca las tecnologías de empaquetado de circuitos integrados en abanico, en abanico con núcleo, en abanico de alta densidad, en 2,5D y en 3D. Sin embargo, sólo se consideran tecnologías "avanzadas" de envasado de semiconductores las que tienen un paso de bumping inferior a 100 µm. Esto incluye las tecnologías de embalaje de circuitos integrados de alta densidad, 2,5D y 3D.

El paso de la integración híbrida 2,5D a la integración vertical 3D completa es crucial para las futuras aplicaciones centradas en los datos, y en este artículo nos centraremos en esta transición.

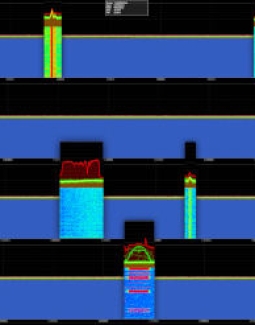

El principal reto en el paso de 2,5D a 3D es escalar el tamaño del paso de bumping. En un encapsulado de CI 2,5D, el tamaño del bump pitch oscila entre 25 µm y 40 µm, según el material del intercalador. Sin embargo, para un encapsulado apilable en 3D, el tamaño de la protuberancia debe reducirse a un solo dígito de µm o incluso por debajo de 1 µm. TSMC ha informado de que el paso de la protuberancia para apilar chips N7/N6 es de 9 µm y de 6 µm para apilar chips N5. Se espera que disminuya a 4,5 µm para el apilamiento de chips N3 y que siga disminuyendo en futuras generaciones de circuitos integrados. El apilamiento de dos chips con un tamaño de bump pitch pequeño plantea un reto importante, ya que debe conseguirse una alineación de alta precisión en los materiales dieléctricos de unión, especialmente a bajas temperaturas. Además, es necesario un control adecuado de los materiales de relleno de Cu para evitar el desbordamiento durante el proceso de unión. Por otra parte, la gestión térmica se convierte en una cuestión crítica para los paquetes con escalas de bumping pequeñas, lo que obliga a considerar diseños de paquetes que permitan una mejor transmisión del calor y posibles tecnologías de refrigeración líquida.

Los motores del crecimiento

IDTechEx ha identificado cuatro áreas de aplicación principales para los envases de semiconductores avanzados: aplicaciones de computación de alto rendimiento (HPC)/centros de datos, redes de comunicación, coches autónomos y electrónica de consumo. La creciente demanda de procesamiento de datos es la principal fuerza impulsora del crecimiento en estas áreas de aplicación. Sin embargo, cada aplicación tiene unos requisitos específicos que requieren tecnologías de envasado de semiconductores avanzadas diferentes.

En el caso de las aplicaciones HPC y los centros de datos, la prioridad es ofrecer una capacidad superior de procesamiento de datos, por lo que las tecnologías 2.5DIC que utilizan intercaladores de Si o puentes de Si son la opción preferida, a pesar de su mayor coste. En cambio, la electrónica de consumo, como los smartphones o los smartwatches, se centra en la miniaturización y el coste, por lo que las tecnologías de encapsulado de base orgánica son la primera opción.

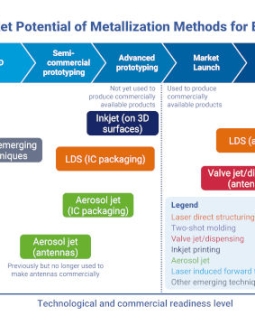

En las comunicaciones 5G y posteriores, el principal reto es la pérdida de transmisión. De ahí que se utilicen tecnologías de embalaje avanzadas para acercar la antena al chip IC de RF y minimizar la pérdida de transmisión. La "antena en paquete (AiP)" es actualmente la opción más viable para 5G mmWave, mientras que la "antena en chip/oblea (AoP)" sigue desarrollándose intensamente para reducir costes.

Para los futuros vehículos autónomos, la integración heterogénea de CPU y otros componentes, como HBM y sistemas fiables de suministro de energía, creará nuevas oportunidades para el envasado y la innovación de semiconductores avanzados.

La expansión del procesamiento de datos es el factor unificador del crecimiento de todas estas aplicaciones. Sin embargo, como los requisitos de cada área de aplicación difieren, se están utilizando tecnologías avanzadas de envasado de semiconductores para satisfacer necesidades específicas.

Autor: Yu-Han Chang, analista tecnológico de IDTechEx

Articulos Electrónica Relacionados

- Ingenieros del MIT diseñan "es... Nuestros músculos son los actuadores perfectos de la naturaleza: dispositivos que transforman la energía en movimiento. Por su tamaño, las fibras musculares son...

- El cargador tipo C reinará en ... El pasado martes, 7 de junio, el Parlamento Europeo y el Consejo llegaron a un acuerdo político para exigir, de forma obligatoria, que los dispositivos electrón...

- Ingenieros del MIT diseñan una... Ingenieros del MIT han desarrollado una réplica robótica de la cavidad derecha del corazón, que imita los latidos y la acción de bombeo de la sangre de los cora...

- La robótica es el futuro del n... Los productos químicos de protección de cultivos y la robótica parecen, a primera vista, totalmente sin relación, sin embargo, IDTec...

- Robots y drones agrícolas se c... La tecnología robótica está transformando silenciosamente el mundo de la agricultura. En este artículo, describimos cómo crec...

- Importancia geoestratégica de ... Un estudio realizado por un equipo de investigadores de la ETSI de Minas y Energía de la Universidad Politécnica de Madrid (UPM) ha analizado las materias prima...

- El mercado de CIs para automoc... Los sistemas que ayudan, automatizan y se comunican, están aumentando el contenido de CIs en los nuevos vehículos de lujo y básicos. A fina...

- Una nueva tecnología que usa p... Los ingenieros de la Universidad Estatal de Oregón han inventado una manera de fabricar plata, un metal altamente conductor, para la electrónica impresa que se ...

- Nagase e Inkron colaboran en n... Nagase & Co., Ltd. y Nagase ChemteX Corporation e Inkron han anunciado el inicio del desarrollo y la colaboración de fabricación para el &aacu...

- Materiales orgánicos para crea... Reducir los costes de producción y, al mismo tiempo, poner en marcha la responsabilidad social y medioambiental, es el fin del proyecto SOLARFLEX, impulsado por...

- Laboratorio de componentes lig... AIMPLAS, Instituto Tecnológico del Plástico, trabaja en un nuevo laboratorio para desarrollar componentes ligeros para vehículos con sensores integrados dentro ...

- Proyecto SELFY para proteger l... Ficosa participa en el consorcio de SELFY, un nuevo proyecto que nace para mejorar la resiliencia de los vehículos autónomos y conectados frente a ciberataques ...