Chip para salvaguardar los datos de los usuarios y computación eficiente en un smartphone

Las aplicaciones de seguimiento de la salud pueden ayudar a las personas a controlar enfermedades crónicas o a mantenerse en forma sin más ayuda que un teléfono inteligente. Sin embargo, estas aplicaciones pueden ser lentas y poco eficientes desde el punto de vista energético, ya que los enormes modelos de aprendizaje automático que las alimentan deben desplazarse entre un teléfono inteligente y un servidor de memoria central.

Los ingenieros suelen acelerar las cosas utilizando hardware que reduce la necesidad de mover tantos datos de un lado a otro. Aunque estos aceleradores de aprendizaje automático pueden agilizar el cálculo, son susceptibles de que los atacantes roben información secreta.

Para reducir esta vulnerabilidad, investigadores del MIT y del MIT-IBM Watson AI Lab crearon un acelerador de aprendizaje automático resistente a los dos tipos de ataques más comunes. Su chip puede mantener en privado los historiales médicos, la información financiera u otros datos confidenciales de un usuario, al tiempo que permite que enormes modelos de IA se ejecuten de forma eficiente en los dispositivos.

El equipo ha desarrollado varias optimizaciones que permiten una gran seguridad al tiempo que ralentizan ligeramente el dispositivo. Además, la seguridad añadida no afecta a la precisión de los cálculos. Este acelerador de aprendizaje automático podría ser especialmente beneficioso para aplicaciones de IA exigentes como la realidad aumentada y virtual o la conducción autónoma.

Aunque la implantación del chip encarecería ligeramente el dispositivo y lo haría menos eficiente desde el punto de vista energético, a veces merece la pena pagar ese precio por la seguridad, afirma el autor principal, Maitreyi Ashok, estudiante de posgrado de Ingeniería Eléctrica e Informática (EECS) en el MIT.

«Es importante diseñar pensando en la seguridad desde el principio. Si se intenta añadir un mínimo de seguridad una vez diseñado el sistema, resulta prohibitivamente caro. Pudimos equilibrar eficazmente muchas de estas compensaciones durante la fase de diseño", afirma Ashok.

Entre sus coautores figuran Saurav Maji, estudiante de posgrado de EECS; Xin Zhang y John Cohn, del Laboratorio de Inteligencia Artificial MIT-IBM Watson; y el autor principal, Anantha Chandrakasan, director de innovación y estrategia del MIT, decano de la Facultad de Ingeniería y catedrático Vannevar Bush de EECS. La investigación se presentará en la Conferencia de Circuitos Integrados Personalizados del IEEE.

Susceptibilidad de canal lateral

Los investigadores se centraron en un tipo de acelerador de aprendizaje automático llamado computación digital en memoria. Un chip IMC digital realiza cálculos dentro de la memoria de un dispositivo, donde se almacenan las piezas de un modelo de aprendizaje automático tras ser trasladadas desde un servidor central.

El modelo completo es demasiado grande para almacenarlo en el dispositivo, pero al dividirlo en fragmentos y reutilizarlos en la medida de lo posible, los chips IMC reducen la cantidad de datos que deben trasladarse de un lado a otro.

Pero los chips IMC pueden ser vulnerables a los piratas informáticos. En un ataque de canal lateral, un hacker vigila el consumo de energía del chip y utiliza técnicas estadísticas para aplicar ingeniería inversa a los datos mientras el chip computa. En un ataque de sondeo de bus, el pirata informático puede robar bits del modelo y del conjunto de datos sondeando la comunicación entre el acelerador y la memoria externa del chip.

La IMC digital acelera el cálculo realizando millones de operaciones a la vez, pero esta complejidad dificulta la prevención de ataques con las medidas de seguridad tradicionales, afirma Ashok.

Ella y sus colaboradores adoptaron un triple enfoque para bloquear los ataques de canal lateral y de bus-probing.

En primer lugar, emplearon una medida de seguridad en la que los datos de la IMC se dividen en trozos aleatorios. Por ejemplo, un bit cero puede dividirse en tres bits que sigan siendo igual a cero tras una operación lógica. La IMC nunca computa con todos los trozos en la misma operación, por lo que un ataque por canal lateral nunca podría reconstruir la información real.

Pero para que esta técnica funcione, hay que añadir bits aleatorios para dividir los datos. Como la IMC digital realiza millones de operaciones a la vez, generar tantos bits aleatorios implicaría demasiados cálculos. Para su chip, los investigadores encontraron una forma de simplificar los cálculos, facilitando la división efectiva de los datos y eliminando la necesidad de bits aleatorios.

En segundo lugar, impidieron los ataques de «bus-probing» utilizando un cifrado ligero que encripta el modelo almacenado en la memoria externa del chip. Este cifrado ligero sólo requiere cálculos sencillos. Además, sólo descifran los fragmentos del modelo almacenados en el chip cuando es necesario.

En tercer lugar, para mejorar la seguridad, generaron la clave que descifra el cifrado directamente en el chip, en lugar de moverla de un lado a otro con el modelo. Generaron esta clave única a partir de variaciones aleatorias en el chip que se introducen durante la fabricación, utilizando lo que se conoce como una función físicamente no clonable.

«Puede que un cable sea un poco más grueso que otro. Podemos utilizar estas variaciones para obtener ceros y unos de un circuito. Para cada chip, podemos obtener una clave aleatoria que debería ser consistente porque estas propiedades aleatorias no deberían cambiar significativamente con el tiempo", explica Ashok.

Reutilizaron las celdas de memoria del chip, aprovechando las imperfecciones de estas celdas para generar la clave. Esto requiere menos cálculos que generar una clave desde cero.

«Dado que la seguridad se ha convertido en una cuestión crítica en el diseño de dispositivos de borde, es necesario desarrollar una pila de sistemas completa centrada en el funcionamiento seguro. Este trabajo se centra en la seguridad de las cargas de trabajo de aprendizaje automático y describe un procesador digital que utiliza optimización transversal. Incorpora el acceso cifrado a los datos entre la memoria y el procesador, enfoques para prevenir los ataques de canal lateral utilizando la aleatorización y explotando la variabilidad para generar códigos únicos. Estos diseños van a ser fundamentales en los futuros dispositivos móviles", afirma Chandrakasan.

Pruebas de seguridad

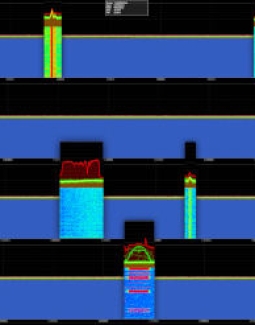

Para probar su chip, los investigadores se pusieron en la piel de piratas informáticos e intentaron robar información secreta mediante ataques de canal lateral y bus-probing.

Incluso después de realizar millones de intentos, no pudieron reconstruir ninguna información real ni extraer fragmentos del modelo o del conjunto de datos. Además, el cifrado seguía siendo indescifrable. En cambio, bastaron unas 5.000 muestras para robar información de un chip desprotegido.

La adición de seguridad redujo la eficiencia energética del acelerador y también requirió una mayor superficie de chip, lo que encarecería su fabricación.

El equipo tiene previsto explorar métodos que puedan reducir el consumo de energía y el tamaño del chip en el futuro, lo que facilitaría su aplicación a gran escala.

«A medida que se vuelve demasiado caro, resulta más difícil convencer a alguien de que la seguridad es fundamental. El trabajo futuro podría explorar estas compensaciones. Quizá podríamos hacerla un poco menos segura, pero más fácil de implantar y menos cara", afirma Ashok.

Articulos Electrónica Relacionados

- Tendencias de automatización i... – Mouser Electronics Inc. lanza hoy el séptimo y último número del galardonado programa Empowering Innovation Together™ 2021. Este último número se sumerge en l...

- Almacenamiento de energía medi... Un equipo de investigadores de la Escuela Técnica Superior de Ingeniería y Diseño Industrial (ETSIDI) de la Universidad Politécnica de Madrid (UPM) ha realizado...

- El aumento de actividad en múl... El mercado global de los controladores lógicos programables (PLC) fue testigo de una fuerte caída en el crecimiento en el 2012 debido a la situación de incertid...

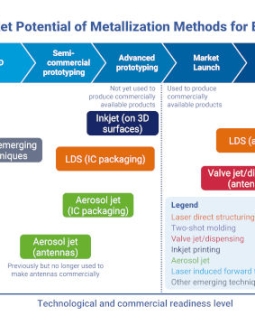

- Nuevos avances en la integraci... La integración de la electrónica en molde IME (In Mold Electronics) es una nueva forma revolucionaria de integrar la electrónica en los plásticos durante el pro...

- Batería de estado sólido sin c... La empresa High Performance Battery (HPB), con sede en Bonn, ha logrado un avance decisivo en la tecnología de baterías y almacenamiento: un equipo dirigido por...

- Tecnología láser aplicable a s... CIC energiGUNE, centro de investigación vasco sobre almacenamiento en baterías, soluciones de energía térmica, e hidrógeno, y Ceit, centro de investigación vasc...

- IoT utilizando chips sin fuent... En el contexto de un proyecto financiado por el FSF (Austrian Science Fund), un grupo de investigadores de Graz analizó un IoT basada en chips RFID sin s...

- El mercado de las ventajas y c... El nuevo informe de IDTechEx, "Electrically Active Smart Glass and Windows 2018-2028" observa que el cristal transparente electicamente activo es una idea que y...

- Primer laboratorio industrial ... El mundo digital y las relaciones comerciales caminan de la mano desde hace más de una década y el nuevo reto al que se enfrentan es conseguir que...

- La electrónica "vestible" (wea... El espacio de dispositivos vestibles es visto como la próxima mina de oro de oportunidades para los fabricantes de sensores, debido a los beneficios se reducen ...

- Las nuevas empresas robóticas ... Los robots agrícolas son un paso natural en la progresión tecnológica de la maquinaria agrícola. De hecho, estamos en tiempos especi...

- Digitalización en el sector ar... Usar máquinas de una manera económica y controlar su utilización es difícil para las pequeñas empresas artesanales. Los sistemas de software convencionales que ...