Chip que reduce el consumo de energía de las redes neuronales hasta en un 95 por ciento

La mayoría de los avances recientes en sistemas de inteligencia artificial, tales como programas de reconocimiento de habla o rostro, han sido cortesía de redes neuronales, mallas densamente interconectadas de procesadores de información simples que aprenden a realizar tareas mediante el análisis de grandes conjuntos de datos de entrenamiento.

Pero las redes neuronales son grandes y sus cálculos consumen mucha energía, por lo que no son muy prácticas para dispositivos de mano. La mayoría de las aplicaciones de teléfonos inteligentes que dependen de redes neuronales simplemente cargan datos en servidores de Internet, que lo procesan y envían los resultados al teléfono.

Ahora, los investigadores del MIT han desarrollado un chip de propósito especial que aumenta la velocidad de los cálculos de red neuronal de tres a siete veces respecto a sus predecesores, al tiempo que reduce el consumo de energía del 94 al 95 por ciento. Eso podría hacer que sea práctico ejecutar redes neuronales localmente en teléfonos inteligentes o incluso integrarlos en los electrodomésticos.

"El modelo del procesador general es que hay una memoria en alguna parte del chip, y hay un procesador en otra parte del chip, y uno mueve los datos hacia adelante y hacia atrás cuando hace estos cálculos", dice Avishek Biswas, estudiante graduado de MIT en ingeniería eléctrica e informática, quien lideró el desarrollo del nuevo chip.

"Dado que estos algoritmos de aprendizaje automático necesitan tantos cálculos, esta transferencia de datos de ida y vuelta es la parte dominante del consumo de energía. Pero el cálculo que estos algoritmos hacen se puede simplificar a una operación específica, llamada el producto punto. Nuestro enfoque fue, ¿podemos implementar esta funcionalidad de producto de punto dentro de la memoria para que no tenga que transferir estos datos de ida y vuelta?

Biswas y su asesor de tesis, Anantha Chandrakasan, decano de la Escuela de Ingeniería del MIT y el Profesor Vannevar Bush de Ingeniería Eléctrica e Informática, describen el nuevo chip en un documento que Biswas presenta esta semana en la conferencia International Solid State Circuits Conference.

Volver a analógico

Las redes neuronales generalmente se organizan en capas. Un único nodo de procesamiento en una capa de la red generalmente recibirá datos de varios nodos en la capa siguiente y pasará datos a varios nodos en la capa superior. Cada conexión entre nodos tiene su propio "peso", que indica qué tan grande será la función de la salida de un nodo en el cálculo realizado por el siguiente. El entrenamiento de la red es una cuestión de establecer esos pesos.

Un nodo que recibe datos de múltiples nodos en la capa siguiente multiplicará cada entrada por el peso de la conexión correspondiente y sumará los resultados. Esa operación, la suma de multiplicaciones, es la definición de un producto punto. Si el producto escalar excede algún valor umbral, el nodo lo transmitirá a los nodos en la siguiente capa, a través de conexiones con sus propios pesos.

Una red neuronal es una abstracción: los "nodos" son solo pesos almacenados en la memoria de un ordenador. El cálculo de un producto escalar generalmente implica recuperar un peso de la memoria, recuperar el elemento de datos asociado, multiplicar los dos, almacenar el resultado en algún lugar y luego repetir la operación para cada entrada a un nodo. Dado que una red neuronal tendrá miles o incluso millones de nodos, se trata de una gran cantidad de datos para moverse.

Pero esa secuencia de operaciones es solo una aproximación digital de lo que ocurre en el cerebro, donde las señales que viajan a lo largo de múltiples neuronas se encuentran en una "sinapsis", o un espacio entre haces de neuronas. Las tasas de activación de las neuronas y las señales electroquímicas que cruzan la sinapsis corresponden a los valores de datos y ponderaciones. El nuevo chip de los investigadores del MIT mejora la eficiencia replicando el cerebro con más fidelidad.

En el chip, los valores de entrada de un nodo se convierten en voltajes eléctricos y luego se multiplican por los pesos adecuados. Solo los voltajes combinados se convierten nuevamente en una representación digital y se almacenan para su posterior procesamiento.

De esta forma, el chip puede calcular productos de puntos para múltiples nodos, 16 a la vez, en el prototipo, en un solo paso, en lugar de desplazarse entre un procesador y la memoria para cada cálculo.

Todo o nada

Una de las claves del sistema es que todos los pesos son 1 o -1. Eso significa que pueden implementarse dentro de la memoria como simples switches que cierran un circuito o lo dejan abierto. El trabajo teórico reciente sugiere que las redes neuronales entrenadas con solo dos pesas deberían perder poca precisión, en algún lugar entre 1 y 2 por ciento.

La investigación de Biswas y Chandrakasan lleva a cabo esa predicción. En experimentos, ejecutaron la implementación completa de una red neuronal en una computadora convencional y el equivalente de peso binario en su chip. Los resultados de su chip generalmente estaban dentro del 2 al 3 por ciento de la red convencional.

Autor: Larry Hardesty, Oficina de Noticias del MIT

Articulos Electrónica Relacionados

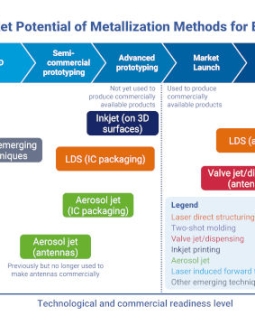

- La electrónica híbrida flexibl... El analista de tecnología IDTechEx, Dr. Matthew Dyson, ha publicado recientemente el siguiente artículo sobre electrónica híbrida flexible. Este artículo sigue ...

- El creciente mercado de fuente... El mercado de las fuentes de alimentación utilizadas para aplicaciones de iluminación por diodos emisores de luz (LED) se expandirá hasta los 9.000 millones de ...

- Prototipo de Motor eléctrico H... Yamaha Motor ha anunciado que ha desarrollado un motor eléctrico que se sitúa en la cabeza de la industria en términos de rendimiento. Esta unidad está destinad...

- Potencial de los sensores piez... Los sensores de presión impresos son una tecnología consolidada, que se ha utilizado en aplicaciones como los sensores de ocupación de automóviles, los pianos e...

- Artículos técnicos sobre diseñ... La electrónica está cada vez más dominada por los sistemas digitales pero existe una creciente demanda de conocimientos analógicos ya que estos sistemas se debe...

- Los vehículos eléctricos se ha... La sofisticación del diseño y el desarrollo del motor en los automóviles está ahora en un cierto contraste con la aplicación ...

- Método para estimar la eficien... La colaboración entre la Universidad Politécnica de Madrid (UPM) y el Consejo Superior de Investigaciones Científicas (CSIC) ha dado como r...

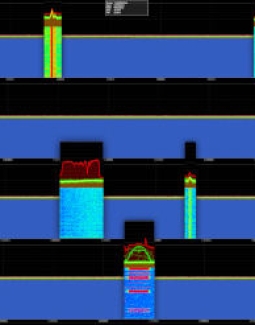

- Alternativas ópticas 3D para t... Una de las principales demandas de la industria 4.0 europea es la disposición de métodos de medición más rápidos y precisos para hacer frente a las nuevas neces...

- Gen 10 y la capacidad de panta... Con BOE, China Star, LG Display y Foxconn esperando construir siete nuevas fábricas de Generation 10.5 para 2020, se espera que la capacidad de fabricaci...

- Oportunidades de diseño del Io... Mouser ha publicado un nuevo libro electrónico en colaboración con Renesas Electronics, donde se explora el uso de la inteligencia artificial (IA) y el aprendiz...

- Micro drones bioinspirados par... Los vehículos aéreos de tamaño reducido han ganado una preponderancia notable en los últimos años debido a sus potenciales aplicaciones en un sinfín de campos, ...

- Investigadores de Luxemburgo p... La investigación dirigida por la Universidad de Luxemburgo investigó el proceso de fabricación de las celdas solares. Los investigadores pr...